# **ISE 4 User Guide**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

CoolRunner, FPGA Architect, FPGA Foundry, Spartan, Timing Wizard, TRACE, Virtex, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

**S**.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCore, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI 64/66, Selectl/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, WebFitter, WebLINX, WebPACK, WebPOWERED, XABEL, XACT*step*, XACT*step*, Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, Xilinx XDTV, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4.758.985; 4.820.937; 4.821.233; 4.835.418; 4.855.619; 4.855.669; 4.902.910; 4.940.909; 4.967.107; 5.012.135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5.500.609: 5.502.000: 5.502.440: 5.504.439: 5.506.518: 5.506.523: 5.506.878: 5.513.124: 5.517.135: 5.521.835: 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5.790.882: 5.795.068: 5.796.269: 5.798.656: 5.801.546: 5.801.547: 5.801.548: 5.811.985: 5.815.004: 5.815.016: 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5.907.245: 5.907.248: 5.909.125: 5.909.453: 5.910.732: 5.912.937: 5.914.514: 5.914.616: 5.920.201: 5.920.202: 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx. Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2001 Xilinx, Inc. All Rights Reserved.

# **About This Manual**

This chapter contains the following sections:

- "About the ISE 4 User Guide"

- "Manual Contents"

- "Additional Resources"

### About the ISE 4 User Guide

The Integrated Synthesis Environment (ISE) from Xilinx is an integrated tool suite that enables you to produce, test, and implement designs for Xilinx FPGAs or CPLDs. The tools cover all aspects of the design flow, from design entry to bitstream generation and downloading. You can directly access the Internet from many of the ISE applications for user support and tool updates.

This ISE 4 User Guide:

- Provides an overview of ISE 4.x.

- Describes the ISE 4.x design environment.

- Explains how to create a project.

- Summarizes each of the steps in the design flow, including design entry, constraint entry, synthesis, simulation, implementation, and device programming.

- Briefly describes each tool in the ISE 4.x suite.

- Provides references to additional help, documentation, and support.

### **Manual Contents**

- Chapter 1, "Introduction," describes ISE in general, lists supported platforms and architectures, and describes partner tools available for use with ISE. It also includes references to sources of additional assistance, including tutorials, books, online help, and technical support.

- Chapter 2, "Project Navigator," describes Project Navigator, the primary user interface for ISE. Project Navigator integrates the design entry, constraint entry, implementation, synthesis, simulation, and device programming tools and processes that facilitate design production.

- Chapter 3, "Projects," describes projects and project management generally, and describes the specific ISE project creation process, which includes specifying a directory for the project, identifying the Xilinx device you want to target for your design, choosing a project flow, and adding and creating source files.

- Chapter 4, "Design Flow," describes the overall design process, including Design Entry, Constraint Entry, Synthesis, Simulation, Implementation, and Device Programming.

- Chapter 5, "HDL," describes HDL design sources (VHDL, Verilog, and ABEL-HDL), the HDL Editor (a general purpose text editor that is HDL language sensitive), and the HDL library mapping feature.

- Chapter 6, "State Diagrams," describes the integration of the supported state diagram entry tools with ISE. For state machine design entry, ISE includes integrated support for StateCAD® and StateBench<sup>™</sup>.

- Chapter 7, "Schematic Sources," explains how to use schematic sources in ISE projects. It also contains an overview of the basic concepts for using the Engineering Capture System (ECS).

- Chapter 8, "LogiBLOX," describes LogiBLOX—a design tool for creating high-level modules such as counters, shift registers, and multiplexers for XC4000/XL/XLA, Spartan/XL, and 9500/XL/ XV designs.

- Chapter 9, "CORE Generator," describes the Xilinx CORE Generator System, a design tool that delivers parameterizeable COREs optimized for Xilinx FPGAs.

- Chapter 10, "Implementation," explains the implementation design process that converts the logical design represented in the source file into a physical file format that can be implemented in the selected target device.

- Chapter 11 "FPGA Implementation," explains the implementation process for FPGA devices, including FPGA Implementation Flow, FPGA Implementation Reports, FPGA Implementation Options, and FPGA Implementation Tools (Floorplanner, FPGA Editor, and Timing Analyzer).

- Chapter 12, "CPLD Implementation," explains the implementation process for CPLD devices, including CPLD Implementation Flow, CPLD Implementation Reports, CPLD Implementation Options, and CPLD Implementation Tools (Timing Analyzer and ChipViewer).

- Chapter 13, "Device Programming," explains how to create a bitstream to download to a device, and describes the programming tools PROM File Formatter and iMPACT.

# **Additional Resources**

For additional information, go to <u>http://support.xilinx.com</u>. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource              | Description and URL                                                                                                                                                                                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials             | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                               |

| Answers Data-<br>base | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                                  |

| Application<br>Notes  | Descriptions of device-specific design techniques and approaches <u>http://support.xilinx.com/apps/appsweb.htm</u>                                                                                                                                                        |

| Data Book             | Pages from <i>The Programmable Logic Data Book</i> , which contains device-<br>specific information on Xilinx device characteristics, including readback,<br>boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |

| Resource       | Description and URL                                                                                                                                  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Xcell Journals | Quarterly journals for Xilinx programmable logic users <u>http://support.xilinx.com/xcell/xcell.htm</u>                                              |

| Technical Tips | Latest news, design tips, and patch information for the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/index.htm |

# Conventions

This manual uses the following conventions. An example illustrates most conventions.

### Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: - 100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

**Courier bold** also indicates commands that you select from a menu.

File  $\rightarrow$  Open

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{ }" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on|off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2 ... locn;

### **Online Document**

The following conventions are used for online documents.

- Blue text indicates cross-references within a book. Red text indicates cross-references to other books. Click the colored text to jump to the specified cross-reference.

- <u>Blue, underlined text</u> indicates a Web site. Click the link to open the specified Web site. You must have a Web browser and Internet connection to use this feature.

# Contents

#### **About This Manual**

| About the ISE 4 User Guide | .ν   |

|----------------------------|------|

| Manual Contents            | .vi  |

| Additional Resources       | .vii |

#### Conventions

| Typographical   | ix |

|-----------------|----|

| Online Document | х  |

#### Chapter 1 Introduction

| About ISE 4.x                   | 1-1 |

|---------------------------------|-----|

| Xilinx Architecture Support     | 1-2 |

| Installation                    |     |

| Partner Tools                   |     |

| Tutorials                       |     |

| ISE Tutorial                    |     |

| In-Depth Tutorial               |     |

| Other Tutorials                 |     |

| Online Help                     |     |

| Context Sensitive Help          | 1_4 |

| Project Navigator Help Contents |     |

| ISE Help Contents               |     |

| Design Entry                    |     |

| Synthesis                       |     |

| Simulation                      |     |

| Implementation                  | -   |

|                                 |     |

| Programming                     |     |

| Techniques                      |     |

| Tutorials                       |     |

| Application Notes               |     |

| Reference                       |     |

| How to Use Help                 |     |

| Online Documentation            |     |

| Xilinx on the Web               |     |

| Books                           |     |

| Printed Books                   | 1-8 |

| Online PDF Book Collection              | 1-8  |

|-----------------------------------------|------|

| Technical Support                       |      |

| Xilinx Services and Support on the Web  | 1-8  |

| Technical and Applications Case Support | 1-9  |

| Training                                | 1-9  |

| Order Management                        | 1-10 |

| Software Customer Service (Licensing)   | 1-10 |

#### Chapter 2 Project Navigator

| About Project Navigator                             | 2-1  |

|-----------------------------------------------------|------|

| Project Navigator Processes                         | 2-1  |

| Project Navigator Tools                             | 2-2  |

| Starting Project Navigator                          | 2-3  |

| Project Navigator Interface                         | 2-3  |

| Project Navigator Main Window                       | 2-4  |

| Sources In Project Window                           | 2-6  |

| Menus                                               |      |

| Sources in Project Window Tabs                      | 2-8  |

| Source Properties                                   | 2-9  |

| Processes for Current Source Window                 | 2-9  |

| Auto-Make                                           |      |

| Setting Properties for Processes                    | 2-10 |

| Viewing Reports                                     | 2-11 |

| Project Workspace                                   | 2-11 |

| HDL Editor Workspace                                | 2-11 |

| Transcript Window                                   | 2-12 |

| Customizing Project Navigator                       | 2-12 |

| Setting Display Preferences                         | 2-12 |

| General                                             | 2-13 |

| Editor                                              |      |

| Processes                                           |      |

| Partner Tools and Web Browser                       | 2-14 |

| Displaying and Hiding Windows and Toolbars          | 2-14 |

| Docking and Undocking Windows and Toolbars          | 2-15 |

| Snapshots and Archives                              | 2-15 |

| Taking a Snapshot                                   | 2-16 |

| Renaming a Snapshot                                 | 2-16 |

| Editing a Snapshot Comment                          | 2-16 |

| Deleting a Snapshot                                 | 2-17 |

| Viewing Snapshot Contents                           | 2-17 |

| Viewing Snapshot Source Files and Reports           | 2-18 |

| Replacing the Current Project with a Snapshot       | 2-18 |

| Restoring a Snapshot or Archive with Remote Sources | 2-19 |

#### Chapter 3 Projects

| About Projects                          | 3-1 |

|-----------------------------------------|-----|

| Creating a Project                      |     |

| Setting Project Properties              | 3-3 |

| Specifying a Project Name and Directory |     |

| Specifying a Project Name and Directory | 3-3 |

| Selecting a Device and Design Flow  | 3-4  |

|-------------------------------------|------|

| Selecting a Device                  | 3-4  |

| Selecting a Design Flow             | 3-5  |

| Supported Devices and Design Flows  | 3-5  |

| Project Flow Characteristics        | 3-6  |

| Sources                             | 3-8  |

| Creating a New Source               |      |

| Adding an Existing Source           |      |

| Adding a Copy of an Existing Source |      |

| Source Types                        | 3-11 |

| Synthesis Tool Support              |      |

| Source Type Descriptions            | 3-13 |

| State Diagram                       | 3-14 |

| Schematic                           | 3-14 |

| VHDL Module                         |      |

| VHDL Testbench                      |      |

| Testbench Waveform                  |      |

| VHDL Package                        |      |

| VHDL Library                        |      |

| Verilog Module                      |      |

| Verilog Test Fixture                |      |

| ABEL-HDL Module (CPLDs Only)        |      |

| ABEL Test Vector (CPLDs Only)       | 3-16 |

| CORE Generator Module               | 2 16 |

|                                     |      |

| LogiBLOX Module                     |      |

# Chapter 4 Design Flow

| About Design Flow                 | 4-1  |

|-----------------------------------|------|

| About Design Flow<br>Design Entry | 4-2  |

| HDL Editor                        | 4-2  |

| StateCAD State Machine Editor     | 4-3  |

| Engineering Capture System (ECS)  |      |

| CORE Generator                    |      |

| LogiBLOX                          |      |

| Constraint Entry                  |      |

| Constraint Types                  |      |

| Third Party Constraints           | 4-5  |

| Constraint Entry Tools            | 4-5  |

| Synthesis                         | 4-6  |

| XST from Xilinx                   | 4-6  |

| FPGA Express from Synopsis        | 4-6  |

| Synplify from Synplicity          | 4-7  |

| LeonardoSpectrum from Exemplar    | 4-7  |

| Simulation                        | 4-8  |

| Simulation Points                 | 4-8  |

| Simulation Tools                  | 4-8  |

| Implementation                    | 4-9  |

| Floorplanner                      | 4-9  |

| FPGÅ Editor                       | 4-10 |

| Timing Analyzer     | 4-10 |

|---------------------|------|

| XPower              | 4-11 |

| ChipViewer          | 4-11 |

| Device Programming  | 4-12 |

| iMPĂCT              | 4-12 |

| PROM File Formatter | 4-13 |

|                     |      |

#### Chapter 5 HDL

| HDL Sources                                                          | 5-  | 1  |

|----------------------------------------------------------------------|-----|----|

| Supported Languages                                                  | 5-  | 1  |

| VHDL                                                                 | 5-  | 2  |

| Verilog                                                              |     |    |

| ABEL-HDL                                                             |     | 2  |

| Creating HDL Source Files                                            | 5-  | 3  |

| New Source Wizard                                                    | 5-3 | 3  |

| Creating New HDL Modules                                             | 5-  | 3  |

| Creating a New VHDL Package                                          | 5-  | 4  |

| Opening HDL Source Files                                             | 5-  | 5  |

| HDL Editor                                                           | 5-  | 6  |

| HDL Editor Functions                                                 | 5-  | 6  |

| HDL Editor Online Help                                               | 5-  | 6  |

| File Operations<br>Window Operations                                 | 5-  | 7  |

| Window Operations                                                    | 5-  | 7  |

| Editing Functions                                                    | 5-  | 8  |

| Search Functions                                                     | 5-  | 8  |

| Macro Functions                                                      |     |    |

| Customizing Tabs and Fonts                                           | 5-  | 9  |

| Language Specific Features                                           | 5-  | 9  |

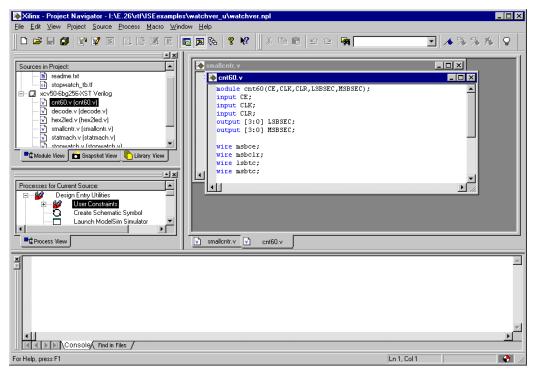

| Language Templates                                                   | 5-  | 9  |

| Opening the Language Templates Tool                                  | 5-  | 10 |

| Selecting an Existing Template<br>Inserting Templates in HDL Sources | 5-  | 11 |

| Inserting Templates in HDL Sources                                   | 5-  | 11 |

| Creating a User Template                                             | 5-  | 12 |

| Creating a Schematic Symbol from an HDL Source                       | 5-  | 13 |

| HDL Library Mapping                                                  | 5-  | 14 |

| VHDL                                                                 |     |    |

| Verilog                                                              | 5-  | 14 |

| Project Navigator Source Libraries                                   | 5-  | 15 |

| Named VHDL Libraries                                                 | 5-  | 16 |

| Adding a File to the Library                                         | 5-  | 16 |

| Renaming VHDL Libraries                                              | 5-  | 16 |

| Removing VHDL Libraries                                              | 5-  | 17 |

| Moving Files to a Library                                            | 5-  | 17 |

| Removing Files from a Library                                        | 5-  | 17 |

#### Chapter 6 State Diagrams

| About StateCAD and StateBench      | .6-1 |

|------------------------------------|------|

| Creating a New State Diagram       | .6-2 |

| Updating an Existing State Diagram |      |

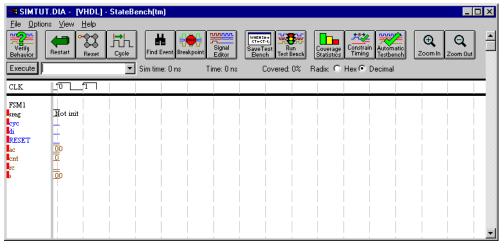

| Using StateBench                    | 6-5 |

|-------------------------------------|-----|

| Instantiating State Diagram Modules | 6-5 |

# Chapter 7 Schematic Sources

| Schematic Source Files                                                                                      | 7-1  |

|-------------------------------------------------------------------------------------------------------------|------|

| Creating a Schematic Source File                                                                            | 7-2  |

| Opening a Schematic Source File                                                                             | 7-4  |

| Updating Schematic Files                                                                                    | 7-4  |

| Xilinx Implementation Attributes and Constraints                                                            | 7-4  |

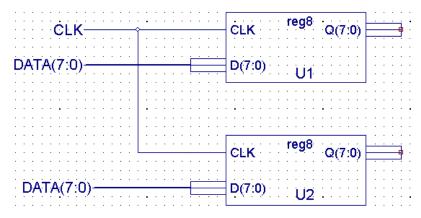

| Instantiating HDL Sources<br>Creating a Schematic Symbol<br>Symbol Generator Options                        | 7-5  |

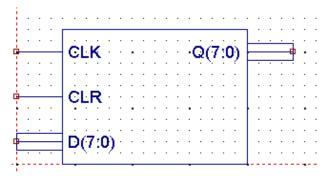

| Creating a Schematic Symbol                                                                                 | 7-5  |

| Symbol Generator Options                                                                                    | 7-5  |

| Opening the HDL Source<br>Creating a Top-Level Schematic                                                    | 7-6  |

| Creating a Top-Level Schematic                                                                              | 7-6  |

| Simulating and Synthesizing Schematic Sources                                                               | 7-7  |

| VHDL Functional Model                                                                                       | 7-8  |

| Simulating and Synthesizing Schematic Sources<br>VHDL Functional Model<br>Viewing the VHDL Functional Model | 7-8  |

| Verilog Functional Model                                                                                    | 7-9  |

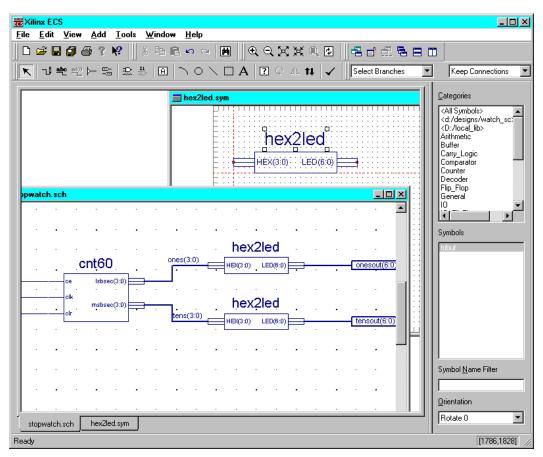

| Verilog Functional Model<br>ECS (Engineering Capture System)                                                | 7-11 |

| The ECS Window                                                                                              | 7-12 |

| The ECS Window<br>Concepts Required to Use ECS                                                              | 7-15 |

| Symbols                                                                                                     |      |

| Symbols<br>Wires (Nets and Buses)                                                                           | 7-18 |

| I/O Markers                                                                                                 | 7-20 |

| Graphics                                                                                                    |      |

| Text                                                                                                        |      |

| ECS Menu Commands                                                                                           |      |

| File Menu                                                                                                   |      |

| Edit Menu                                                                                                   | 7-22 |

| View Menu                                                                                                   |      |

| Add Menu                                                                                                    |      |

| Tools Menu                                                                                                  | 7-23 |

| Window Menu                                                                                                 |      |

| Help Menu                                                                                                   |      |

| Editing Schematics in ECS                                                                                   |      |

| Adding a Symbol                                                                                             |      |

| Adding a Wire                                                                                               | 7-25 |

| Moving a Wire                                                                                               |      |

| Moving a Wire Without Disconnecting                                                                         |      |

| Moving and Disconnecting a Wire                                                                             | 7-26 |

| Removing a Symbol or Other Object<br>Panning<br>Zooming                                                     |      |

| Panning                                                                                                     |      |

| Zooming                                                                                                     | 7-27 |

| Editing Symbols in ECS                                                                                      | 7-27 |

| Opening a Symbol Window                                                                                     |      |

| Opening a Symbol Window<br>Symbol Types                                                                     | 7-28 |

| Block Symbols                                                                                               | 7-28 |

| Graphic Symbols                                                                                             | 7-28 |

| Master Symbols                                                                                              |      |

|                                                                                                             |      |

| Symbol Libraries                         | 7-29 |

|------------------------------------------|------|

| Modifying an Existing Symbol             | 7-29 |

| Creating a New Block Symbol              | 7-30 |

| Creating a Block Symbol from a Schematic | 7-31 |

| Creating a Symbol from an HDL Source     | 7-31 |

| Using Symbols from Other Projects        | 7-32 |

| Guidelines for Creating Schematics       | 7-33 |

# Chapter 8 LogiBLOX

| About LogiBLOX                                  | .8-1  |

|-------------------------------------------------|-------|

| Starting LogiBLOX                               | .8-2  |

| LogiBLOX Setup                                  | .8-4  |

| Creating LogiBLOX Modules                       | .8-5  |

| Using LogiBLOX Modules in ISE 4.x Projects      | .8-7  |

| Editing LogiBLOX Modules                        | .8-7  |

| Using LogiBLOX Modules in Schematic Sources     | .8-7  |

| Instantiating LogiBLOX Modules in an HDL Source | .8-8  |

| VHDL Instantiation                              | .8-8  |

| Verilog Instantiation                           | .8-14 |

| Simulating LogiBLOX Components                  | .8-18 |

| Constraining LogiBLOX Memory with FPGA Express  | .8-18 |

| Estimating the Number of Primitives Used        | .8-19 |

| How the RAM Primitives are Named                |       |

| Referencing a LogiBLOX Module or Component      |       |

| Referencing the Primitives of a LogiBLOX Module |       |

| Verilog Example                                 | .8-21 |

| test.v:                                         | .8-21 |

| inside.v:                                       |       |

| test.ucf                                        |       |

| VHDL Example                                    | .8-23 |

| test.vhd                                        |       |

| inside.vhd                                      | -     |

| test.ucf                                        |       |

| LogiBLOX Documentation                          | .8-25 |

#### Chapter 9 CORE Generator

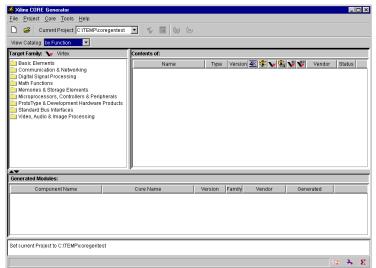

| About CORE Generator                     | 9-1 |

|------------------------------------------|-----|

| Design Flow                              |     |

| Opening the CORE Generator Main GUI      |     |

| Creating a CORE Component                | 9-4 |

| CORE Component Names                     | 9-6 |

| Using Cores in ISE 4 Projects            | 9-7 |

| Editing Cores                            |     |

| Using Cores in Schematic Sources         |     |

| Instantiating Cores in an HDL Source     | 9-8 |

| Simulation and Synthesis of Core Modules | 9-8 |

| Synthesizing and Simulating Cores        | 9-9 |

|                                          |     |

#### Chapter 10 Implementation

| About Implementation                  | 10-1 |

|---------------------------------------|------|

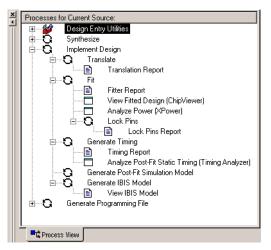

| Implementing Design Processes         | 10-2 |

| Implementing Your Design              |      |

| Complete Implementation               |      |

| Partial Implementation                |      |

| Specialized Processing                |      |

| Implementation Errors and Warnings    |      |

| Saving Implementation Results         | 10-4 |

| Deleting Results                      | 10-4 |

| Changing Devices                      |      |

| Viewing Implementation Reports        |      |

| Generating and Viewing a Report       |      |

| Report Descriptions                   |      |

| User Constraints                      |      |

| Editing the UCF File                  | 10-6 |

| Opening the Xilinx Constraints Editor |      |

#### Chapter 11 FPGA Implementation

| Flow                                          | 11-1  |

|-----------------------------------------------|-------|

| Translate                                     | 11-3  |

| MAP                                           | 11-4  |

| Generate Post-Map Static Timing (Optional)    | 11-6  |

| Place and Route                               | 11-7  |

| Generate Post-Place & Route Timing (Optional) | 11-9  |

| Multi Pass Place and Route (Optional)         |       |

| Backannotate Pin Locations (Optional)         | 11-11 |

| Backannotate Pin Locs Report                  | 11-12 |

| Pin Loc Constraints in the UCF                | 11-12 |

| Reports                                       | 11-13 |

| Properties                                    | 11-14 |

| Opening the Process Properties Dialog Box     |       |

| Accessing Advanced Properties                 | 11-16 |

| Tools                                         | 11-16 |

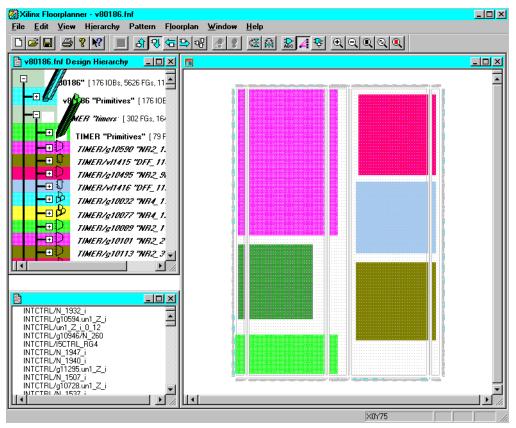

| Floorplanner                                  | 11-17 |

| FPGA Editor                                   | 11-19 |

| Timing Analyzer                               | 11-20 |

| XPower                                        |       |

| Why Estimate Power?                           |       |

| XPower Prerequisites                          |       |

| Features of XPower                            | 11-23 |

|                                               |       |

#### Chapter 12 CPLD Implementation

| Implement Design            |  |

|-----------------------------|--|

| Translate                   |  |

| About the Translate Process |  |

| Translation Report          |  |

| •                           |  |

| Fit                                              | 12-4  |

|--------------------------------------------------|-------|

| About the Fit Process                            | 12-4  |

| Fitter Report                                    | 12-6  |

| View Fitted Design (ChipViewer)                  | 12-6  |

| Analyze Power (XPower)                           | 12-6  |

| Lock Pins                                        | 12-7  |

| Generate Timing                                  | 12-10 |

| Timing Report                                    |       |

| Analyze Post-Fit Static Timing (Timing Analyzer) | 12-11 |

| Generate Post-Fit Simulation Model               | 12-11 |

| Generate IBIS Model                              | 12-11 |

| Properties                                       | 12-12 |

| Opening the Process Properties Dialog Box        | 12-12 |

| Setting Options                                  | 12-13 |

| Translate Options                                | 12-13 |

| Fit Options                                      | 12-14 |

| Lock Pins Options                                | 12-14 |

| Timing Options                                   |       |

| Tools                                            |       |

| Timing Analyzer                                  | 12-15 |

| CPLD Chip Viewer                                 |       |

| For Pin Assignments                              | 12-17 |

| View Fitted Design (ChipViewer)                  | 12-17 |

|                                                  |       |

# Chapter 13 Device Programming

| Creating FPGA Programming Files                | 13-1 |

|------------------------------------------------|------|

| Launching Programming Tools                    | 13-2 |

| Setting FPGA Programming File Creation Options |      |

| Generating CPLD Programming Files              | 13-3 |

| Setting CPLD Programming File Creation Options | 13-4 |

| Device Programming Tools                       | 13-5 |

| PROM File Formatter                            | 13-5 |

| iMPACT                                         | 13-5 |

|                                                |      |

# **Chapter 1**

# Introduction

This chapter contains the following sections:

- "About ISE 4.x"

- "Xilinx Architecture Support"

- "Installation"

- "Partner Tools"

- "Tutorials"

- "Online Help"

- "Books"

- "Technical Support"

### About ISE 4.x

ISE 4.x from Xilinx is a next-generation design environment for programmable logic design. It offers advanced software capabilities that enable designers to efficiently create and verify programmable logic design. Features include:

- HDL Design Entry and Project Management Tools

- HDL Synthesis Engines from Synopsys<sup>®</sup> and Xilinx

- Incremental Design with Block Level Incremental Synthesis (BLIS)

- Seamless integration with Synplify<sup>™</sup> from Synplicity

- Seamless integration with LeonardoSpectrum from Exemplar

- Xilinx Ultra-fast Place and Route

- Customizable Intellectual Property Using CORE Generator

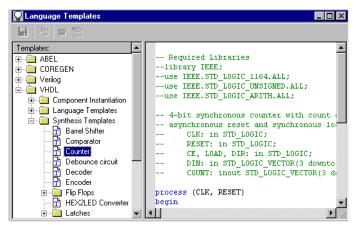

- Graphical State Diagram Entry Using StateCAD

- Seamless Integration with ModelSim<sup>™</sup> HDL Simulation Tools

- Automatic Self-checking Testbench Generation Using HDL Bencher

# Xilinx Architecture Support

For a list of the most current supported device families and device flows, see the Device Support table in the ISE online help (Help  $\rightarrow$  ISE Help Contents  $\rightarrow$  Reference  $\rightarrow$  Device Support). The devices available for your design depend upon the product configuration you purchased, and on the design flow you select for your project.

### Installation

For instructions on installing ISE 4.x, see the *ISE Installation Guide and Release Notes*. This document accompanies your software, and is also available on the Xilinx support Web site at <a href="http://www.support.xilinx.com/">http://</a> www.support.xilinx.com/ under Software Manuals. It describes installation procedures, key features, supported devices, and the most critical known issues.

### **Partner Tools**

ISE 4.x supports the following partner tools to provide a complete design environment:

• FPGA Express from Synopsys<sup>®</sup>

FPGA Express is integrated into the design flows of ISE 4.x to provide synthesis functions as it has in earlier products.

• ModelSIM<sup>™</sup> from Model Technology Incorporated (MTI)

ModelSIM simulators provide the simulation functions for ISE 4.x.

LeonardoSpectrum from Exemplar

LeonardoSpectrum is a synthesis tool that synthesizes VHDL or Verilog and creates an EDIF netlist. An interface into this tool is provided in ISE 4.x. However, in order to use LeonardoSpectrum with ISE, you must have purchased and installed the program on your computer.

• Synplify and Synplify Pro from Synplicity

Synplify and Synplify Pro are synthesis tools designed for FPGA synthesis with VHDL, Verilog and mixed languages to create an EDIF netlist. In order to use either tool with ISE, you must separately purchase and install the program on your computer.

### **Tutorials**

Several tutorials are available to assist you in learning ISE 4.x:

- "ISE Tutorial"

- "In-Depth Tutorial"

- "Other Tutorials"

#### **ISE Tutorial**

The *ISE Tutorial* is a printed booklet distributed with your ISE software. It describes the creation of a 4-bit counter module. The tutorial includes:

- creating HDL and schematic source files for the design

- functionally simulating the design's logic

- processing the design for device implementation

- using basic timing simulation to test the design in the device

#### **In-Depth Tutorial**

An in-depth tutorial, the Watch tutorial, is available on the Xilinx support Web site from <u>http://support.xilinx.com/support/techsup/tutorials/index.htm</u>.

#### **Other Tutorials**

The following tutorials are available from the Project Navigator online help:

- CPLD Design Flows

- XPower FPGA Tutorial

- XPower CPLD Tutorial

### **Online Help**

The following online help is available from Project Navigator and its associated tools. To access the help, click the Help menu, or press **F1**.

- "Context Sensitive Help"

- "Project Navigator Help Contents"

- "ISE Help Contents"

- "How to Use Help"

- "Online Documentation"

- "Xilinx on the Web"

#### **Context Sensitive Help**

Context sensitive help is available for all ISE 4.x tools. To access context sensitive help, press F1.

#### **Project Navigator Help Contents**

To access help for Project Navigator as a whole, select  $\texttt{Help} \rightarrow \texttt{Project Navigator Help Contents}$ .

#### **ISE Help Contents**

The ISE Help umbrella lists all help files available from within Project Navigator. To access the ISE help umbrella, select  $\texttt{Help} \rightarrow \texttt{ISE}$  Help Contents. When the umbrella opens, click a link to access the

indicated help or other support file. The umbrella help menu includes links to the following:

#### **Design Entry**

- Project Navigator

- HDL Editor

- StateCAD State Machine Editor

- Schematic Editor (ECS)

- LogiBLOX

- CORE Generator

- Xilinx Constraints Editor

#### Synthesis

- XST (Xilinx Synthesis Technology)

- FPGA Express

- Synplify

- LeonardoSpectrum

#### Simulation

- HDL Bencher

- ModelSim Simulator

#### Implementation

- Floorplanner

- FPGA Editor

- Timing Analyzer

- XPower

- ChipViewer

**Note** Chip Viewer help can be accessed from the Chip Viewer window only.

#### Programming

- iMPACT

- PROM File Formatter

#### **Techniques**

- FPGA Design Techniques

- CPLD Design Techniques

- Entering Constraints

#### Tutorials

- ISE Tutorial

- In-Depth Tutorial

- CPLD Design Flows

- XPower FPGA Tutorial

- XPower CPLD Tutorial

For more information, see the "Tutorials" section above.

#### **Application Notes**

• ISE Application Notes

**Note** For current versions of ISE Application Notes, see <u>http://</u><u>www.xilinx.com/apps/appsweb.htm</u>

• FPGA Express Application Notes

#### Reference

- ISE 4.x Key Features

- Device Support

- Product Licensing

- VHDL Reference Guide

- Verilog Reference Guide

- ABEL Reference Guide

- CPLD Schematic Library

- CPLD Attributes

- Technical Support

#### How to Use Help

How to Use Help is a Microsoft Windows tutorial which explains how to use an online help file.

#### **Online Documentation**

Click the Online Documentation link to open the book collection that accompanies your ISE 4.x software. For more information, see the "Books" section below.

#### Xilinx on the Web

To access Xilinx services on the World Wide Web, click  $\texttt{Help} \rightarrow \texttt{Xilinx}$  on the Web, then select one of the following:

• Xilinx Home Page

The Home Page for programmable logic. From this page, you can obtain more information about Xilinx products, access online support and services, enroll in Xilinx e-Learning, buy Xilinx products online, and much more.

- LogiCORE PCI Solutions The Xilinx 64-bit, 66 MHz PCI-X Solution to support next generation communication systems and storage area networks.

- Support and Services Support and Services takes you to the Xilinx Support page at <u>http://support.xilinx.com</u>.

- Open a Support Case Allows you to open a personal WebCase with Xilinx Support.

For more information about Xilinx support available on the Web, by telephone and e-mail, see the "Technical Support" section below.

# Books

Multiple printed and online books are available for use with your ISE 4.x software.

#### **Printed Books**

The following hardcopy books accompany your ISE 4.x software:

- The *ISE Installation Guide and Release Notes* describes installation procedures, key features, supported devices, and the most critical known issues.

- The *ISE Tutorial* provides an overview of the key features of the ISE 4.x software. It also contains a tutorial that demonstrates the basic design process. The tutorial includes creating HDL and schematic source files for the design, functionally simulating the design's logic, processing the design for device implementation, and using basic timing simulation to test the design in the device.

#### **Online PDF Book Collection**

The online PDF book collection is available for viewing and printing. You can access the online book collection from the Documentation CD or from the Xilinx support page on the Web at <u>http://</u> <u>support.xilinx.com</u>.

### **Technical Support**

You can contact Xilinx for additional information and assistance in a variety of ways.

#### Xilinx Services and Support on the Web

Start by getting answers on the Web at <u>http://support.xilinx.com</u>. The support.xilinx.com Web site contains thousands of online technical solutions and product information for Xilinx software and devices. The Xilinx Answers Database is updated daily with the latest patches, problem resolutions, application notes, and data sheets.

### **Technical and Applications Case Support**

If you cannot find your answers at support.xilinx.com, open a support case on the Web to access Xilinx Application Engineers worldwide. You can also use telephone hotlines or e-mail to open a support case.

| Location                   | Phone                              | E-Mail                         |

|----------------------------|------------------------------------|--------------------------------|

| North America              | 1-800-255-7778 or 408-<br>879-5199 | Please open a case via WebCase |

| United Kingdom             | +44-870-7350-610                   | eurosupport@xilinx.com         |

| France                     | +33-1-34-63-01-00                  | eurosupport@xilinx.com         |

| Germany                    | +49-89-93-08-81-30                 | eurosupport@xilinx.com         |

| All other Europe locations | +44-870-7350-610                   | eurosupport@xilinx.com         |

| Japan                      | +81-3-5321-7750                    | jhotline@xilinx.com            |

| Hong Kong                  | (852) 2424-5200                    | hongkong@xilinx.com            |

| Korea                      | (82) 2-761-4277                    | korea@xilinx.com               |

**Note** The above telephone numbers and e-mail address are subject to change. For the most current Technical Support contact information, go to <u>http://support.xilinx.com/support/services/contact\_info.htm</u>.

When e-mailing inquiries, please provide your complete name, company name, phone number, and a complete problem description, including your design entry software and design stage. In North America, call 1-800-255-7778 if you cannot open a support case on the Web.

#### Training

For information on training, visit the Xilinx Support Web site at <u>http://support.xilinx.com</u>, or contact your local Xilinx distributor.

Get information and schedules for all courses, including recorded and live e-Learning modules. Comprehensive introductory and advanced courses cover Xilinx component and development system products.

#### **Order Management**

To order Xilinx products, visit the Xilinx Support Web site at <u>http://support.xilinx.com</u>, or contact your local Xilinx distributor.

#### Software Customer Service (Licensing)

| Location                 | Phone                                    | E-Mail               |

|--------------------------|------------------------------------------|----------------------|

| North America            | 1-800-624-4782 or<br>(408) 879-6127      | isscs@xilinx.com     |

| Europe                   | Contact your local<br>Xilinx distributor | m1license@xilinx.com |

| Japan                    | +81-3-5321-7732                          | cs_1@xilinx.com      |

| All other loca-<br>tions | 1-800-624-4782 or<br>(408) 879-6127      | cs_1@xilinx.com      |

# **Chapter 2**

# **Project Navigator**

This chapter contains the following sections:

- "About Project Navigator"

- "Starting Project Navigator"

- "Project Navigator Interface"

- "Customizing Project Navigator"

- "Snapshots and Archives"

#### About Project Navigator

Project Navigator is the primary user interface for ISE 4.x. You create your FPGA or CPLD design using a suite of tools accessible from Project Navigator. Each step of the design process, from design entry to downloading the design to the chip, is managed from Project Navigator as part of a project. See the "Projects" chapter of this Guide for more information.

#### **Project Navigator Processes**

Project Navigator integrates the following processes, which are described in more detail in the "Design Flow" chapter of this Guide:

- "Design Entry"

- "Constraint Entry"

- "Synthesis"

- "Simulation"

- "Implementation"

- "Device Programming"

# **Project Navigator Tools**

| Tool                                                                                                                                                                      | Function                                     | Reference                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------|

| HDL Editor                                                                                                                                                                | create HDL files                             | "HDL" chapter                                                                                    |

| StateCAD and StateBench                                                                                                                                                   | state machine creation                       | "State Diagrams" chapter                                                                         |

| Engineering Capture<br>System (ECS)                                                                                                                                       | schematic and symbol creation and editing    | "Schematic Sources"<br>chapter                                                                   |

| LogiBLOX                                                                                                                                                                  | design entry                                 | "LogiBLOX" chapter                                                                               |

| CORE Generator                                                                                                                                                            | design entry                                 | "CORE Generator" chapter                                                                         |

| Xilinx Constraints Editor                                                                                                                                                 | constraint entry                             | Xilinx Constraints Guide                                                                         |

| XST (Xilinx Synthesis Tech-<br>nology) from Xilinx<br>FPGA Express from<br>Synopsys<br>LeonardoSpectrum from<br>Exemplar<br>Synplify, and Synplify Pro<br>from Synplicity | synthesis                                    | Xilinx Synthesis and Simula-<br>tion Guide                                                       |

| HDL Bencher                                                                                                                                                               | automated testbench or test fixture creation | Xilinx Synthesis and Simula-<br>tion Guide                                                       |

| ModelSim XE/PE/SE from<br>Model Technology Inc.                                                                                                                           | simulation                                   | Xilinx Synthesis and Simula-<br>tion Guide                                                       |

| FPGA Editor<br>Timing Analyzer<br>Floorplanner<br>ChipViewer<br>XPower                                                                                                    | implementation                               | "Implementation" chapter<br>"FPGA Implementation"<br>chapter<br>"CPLD Implementation"<br>chapter |

| PROM File Formatter<br>iMPACT                                                                                                                                             | programming                                  | "Device Programming" chapter                                                                     |

Project Navigator supports the following tools:

**Note** See the "Books" section of the "Introduction" chapter of this Guide for information on accessing the *Xilinx Constraints Guide* and the *Xilinx Synthesis and Simulation Guide*.

### **Starting Project Navigator**

To start Project Navigator on personal computers:

- Double-click the Project Navigator icon on your desktop. OR

- Click Start  $\rightarrow$  Programs  $\rightarrow$  Xilinx ISE Series 4.x  $\rightarrow$  Project Navigator.

**Note** Your startup menu path is created during installation, and may differ from the path shown above.

To start Project Navigator on workstations:

- 1. Go to the UNIX command prompt.

- 2. Type ise.

The first time you open Project Navigator all of its windows are empty. After that, Project Navigator opens with the last project you worked on if you selected Edit  $\rightarrow$  Preferences  $\rightarrow$  General  $\rightarrow$ Window Settings  $\rightarrow$  Always Open Last Project.

To begin using Project Navigator, you first create a project, then create or add source files for the project. To create a project, click  $\texttt{File} \rightarrow \texttt{New Project}$ . See the "Projects" chapter for the steps to create a new project and to add sources.

### **Project Navigator Interface**

The Project Navigator interface contains the following:

- "Project Navigator Main Window"

- "Sources In Project Window"

- "Processes for Current Source Window"

- "Project Workspace"

- "HDL Editor Workspace"

- "Transcript Window"

#### **Project Navigator Main Window**

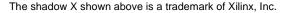

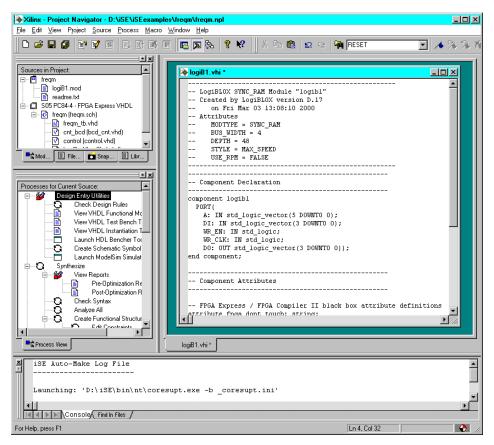

The following figure shows the windows, toolbars, workspaces, and other objects in the Project Navigator main window.

#### Figure 2-1 Project Navigator Main Window

The Project Navigator main window contains the following:

• Title Bar

The Title bar displays the name of the application and the path of the current project.

• Menu Bar

The Menu bar allows you to access the Project Navigator commands. See the Project Navigator online help for a description of all commands. Toolbars

The toolbars provide convenient access to frequently used commands. There are two toolbars in the Project Navigator, a Standard toolbar and an Editor toolbar containing commands performed in the HDL Editor. See the Project Navigator online help for a detailed description of the toolbars.

• "Sources In Project Window"

The Sources in Project window shows all the design files associated with a project. It includes tabs to view the project in Module View, Snapshot View, and Library View.

• "Processes for Current Source Window"

The Processes for Current Source window shows the available processes for the selected source. The processes available for other sources depend upon the device and design flow you selected for the project, as well as the source type.

Note No processes are available for user documents.

• "Project Workspace"

The Project Workspace consists of the Sources in Project window and the Processes for Current Source window.

• "HDL Editor Workspace"

HDL files and text files are created and edited in the HDL Editor workspace. To expand the screen area available for the HDL Editor Workspace, click  $\forall iew \rightarrow \texttt{Project Workspace}$  to toggle the Project Workspace off.

• HDL Editor Window

Each HDL file is opened in its own window within the HDL Editor Workspace.

• "Transcript Window"

The Transcript window:

- Displays informational, warning, and error messages.

- Includes an error and warning navigation feature to help you debug your design.

• Status Bar

The status bar displays command and processing information. Place the mouse pointer over a menu item or toolbar button to see a description of the object in the status bar.

Some tools, such as the Engineering Capture System (ECS), open in their own windows separate from Project Navigator.

#### **Sources In Project Window**

The Sources in Project window lists all the design files associated with a project. A source is any element that contains information about a design definition. Sources include:

- Files necessary to describe the behavior of your design, such as EDIF, schematics, or HDL source files

- Files needed to test your design, such as testbenches, test fixtures, and waveforms for simulation

- General project design documentation

Icons to the left of the source file names identify the type of design source.

There are two lines in the Sources in Project window when it is open in Module View:

- User Document line

- Device and Design Flow line

# Figure 2-2 User Document Line and Device and Design Flow Line

**Note** Click the minus (-) icon to collapse the listings. Click the plus (+) icon to expand the listings.

#### **User Document Line**

The User Document line is the first top-level line in the module hierarchy and is identified by a document icon. It shows the project name and lists all user documents in the project. In the example above, it reads "watchver."

*User document* is a source type used for any file that you want to associate with a design project, but that should not or cannot be processed by ISE 4.x. The most common use of this source type is for text documents (such as TXT, WRI, DOC) that describe the project.

#### Device and Design Flow line

The Device and Design Flow line is the second top-level line in the module hierarchy and is identified by a chip icon. It shows the name of a device and the design flow associated with the device. In the example above, it reads "xcv50-6bg256-XST Verilog."

To change the Device Family, Device, and Design Flow:

- 1. Right-click the Device and Design Flow line.

- 2. Click Properties from the pull-down menu.

- 3. Make your changes in the Project Properties dialog box.

#### Menus

Use the **Project** menu to create, add, and copy project sources. The sources are created or added as described in the "Creating a Project" section of the "Projects" chapter. A source does not appear in the Sources in Project window until it is added to the project.

Use the **Source** menu to manipulate the sources listed in the Sources in Project window. Click a source to select it before accessing the Source menu. The Source menu includes the following selections:

- Open

- Close

- Rename (snapshots and VHDL libraries only)

- Remove

- Move to Library (HDL design files only)

- Properties

All source editors are linked with the Project Navigator. If a source is modified and the modification changes the hierarchy of the design, the Sources in Project window automatically updates to reflect the change.

#### Sources in Project Window Tabs

Tabs at the bottom of the Sources in Project window allow you to select three different views of the source data:

- "Module View"

- "Snapshot View"

- "Library View"

#### Module View

Click Module View to see a hierarchical representation of the design files associated with a project. These are divided into two groups in the window: user documents and project sources.

User documents

User documents are listed above the Device and Design Flow line. User documents do not have any processes associated with them. The Processes for Current Source window is blank when a user document is selected in the Sources in Project window.

• Project sources

Project sources are listed below the Device and Design Flow line in a manner that depicts the relationship of these sources to each other. If you click the Device and Design Flow line or any of the sources below it, the processes that Project Navigator associates with the selected source type are listed in the Processes for Current Source window.

Both groups (project sources and user documents) behave consistently within the Sources in Project window. To view or edit a project source or user document, double-click it.

- If the source is a schematic, the associated editor is the Engineering Capture System (ECS).

- If the source is a VHDL source file, the associated editor is the HDL Editor, the Project Navigator's language sensitive text editor.

• If the user document is a text file, the associated text editor is opened.

#### **Snapshot View**

Click the **Snapshot View** tab to see a list of the snapshots you took to preserve versions of your design. Click the Source menu to open, rename, or remove a snapshot. See the "Snapshots and Archives" section below for complete information on taking and using snapshots.

#### Library View

Click Library View to see a list of the Libraries associated with the project and the sources included in each one. VHDL projects can include multiple libraries. See the "HDL" chapter later in this Guide for information on creating named VHDL libraries and moving modules to a library.

### **Source Properties**

In the Sources in Project window, only the project title and the Device and Design Flow sources have properties associated with them.

To change the project title or the Device and Design Flow:

- 1. Highlight the project title or the Device and Design Flow line in the Sources in Project window.

- 2. Click Source  $\rightarrow$  Properties.

- 3. Change the project title or Device and Design Flow in the Project Properties dialog box.

### **Processes for Current Source Window**

The Processes for Current Source window shows all the processing tasks that apply to the module or file selected in the Sources in Project window. Project Navigator's context sensitive capability automatically determines the design flow options for a source based on the targeted device and synthesis tool. Project Navigator displays only those processes that can be performed on a specific source.

#### Auto-Make

Project Navigator includes an *auto-make* feature that provides resultsoriented processing. You determine the end result of the processing by selecting a process in the Processes for Current Source window. When you click a process, the auto-make feature checks for dependencies between the process you selected and any predecessor processes that may be out of date or that may not have been run.

Auto-make automatically runs the necessary processes to bring your design up-to-date so that it can complete the process you requested. Auto-make reduces design errors by ensuring that each process step operates on the most current process results and design data.

### **Setting Properties for Processes**

Design processes execute other programs or sets of programs. Very often you can set parameters to be passed into these programs. For example, you can set a parameter to insert I/O buffers during synthesis, or one to use zero or maximum delays for a simulation. The most common properties for a given process are selected as the defaults. You do not need to set the process properties to run a process.

To specify properties for a process:

- 1. Highlight the process.

- 2. Click Process  $\rightarrow$  Properties.

The Process Properties dialog box opens containing parameters appropriate for the process.

If no properties can be set for that process, the Properties selection is grayed out. If the Property Name in the dialog box cannot be fully viewed or appears truncated, use the grabber bar to expand the Property Name field. Click OK to preserve the new field length settings.

#### **Viewing Reports**

In many cases, a report is the output of a process. To view a report, double-click its name in the Processes for Current Source window. If the report does not currently exist, it is generated. A green check mark by the report name indicates that the report is up-to-date, and no processing is performed.

If the report is not up-to-date, to update the report before you view it:

- 1. Click the report name.

- 2. Click Process  $\rightarrow$  Run.

The auto-make process automatically runs only the necessary processes to update the report before displaying it.

Click **Process**  $\rightarrow$  **Rerun All** to re-run all processes—even those processes that are currently up-to-date—from the top of the design to the stage where the report would be generated before displaying the report.

Reports on the synthesis process vary depending on the synthesis tool you are using. Reports for the Implement Design process vary depending on whether the target device is an FPGA or a CPLD. See the "Implementation" chapter for descriptions of the implementation reports.

### **Project Workspace**

The Project Workspace consists of the Sources in Project window and the Processes for Current Source window. These windows are grouped together for viewing purposes. Click  $View \rightarrow Project$ Workspace to toggle the display of these two windows as one item.

### **HDL Editor Workspace**

The HDL Editor workspace is the main text editing area for HDL code. It is the only Project Navigator window that cannot be hidden or undocked (see the "Docking and Undocking Windows and Toolbars" section below).

Tabs at the bottom of the HDL Editor workspace allow easy access to the file you want to view or edit. The Window menu provides standard window functions, such as cascading and tiling, for managing open windows. Two toolbars are available in Project Navigator:

- The Standard toolbar (left side of the toolbar area)

- The Editor toolbar (right side of the toolbar area). The Editor toolbar is used exclusively with the files in the HDL Editor workspace.

See the online help for information on using the toolbars. Use the View menu to toggle the toolbars on and off.

### **Transcript Window**

The Transcript window contains a project log. The output of all processes is captured here, including error and warning messages from the synthesis and implementation tools.

If the error or warning was generated by the synthesis tool (XST or FPGA Express), you can go to the line in the VHDL or Verilog source file containing the error.

For all errors and warnings, you can use the search engine on the Xilinx Web site to find a Solution Record pertaining to your problem. For more information on navigating to a source file and navigating to a solution record, see the Transcript window online help.

# **Customizing Project Navigator**

You can customize Project Navigator by:

- "Setting Display Preferences"

- "Displaying and Hiding Windows and Toolbars"

- "Docking and Undocking Windows and Toolbars"

### **Setting Display Preferences**

Click Edit  $\rightarrow$  Preferences to open the Preferences dialog box. The Preferences dialog box contains four tabs:

- "General"

- "Editor"

- "Processes"

- "Partner Tools and Web Browser"

#### General

From the General tab you can set:

- Window settings, including Always Open Last Project and Use File Associations on User Documents (personal computers only)

- The default path for new sources, including Relative Paths and Absolute Paths

- The project font (the font used in the Sources in Project and Processes for Current Source windows)

#### Editor

From the Editor tab, you can select:

- Attributes for tabs

- The font used in HDL Editor windows

#### Processes

From the Processes tab, you can specify:

- "Property Display Level"

- "Process Tree Default"

#### Property Display Level

You can set process properties for processes such as simulation, synthesis, or implementation. The available properties are displayed in a Process Properties dialog box. You control whether to include additional advanced properties in the Process Properties list. By default, only the standard properties are listed.

Standard displays all of the Standard properties and their default values in the Process Properties dialog boxes. Advanced displays all of the Standard properties as well as any Advanced properties and their default values in the Process Properties dialog boxes.

#### **Process Tree Default**

Determines the default hierarchical display of processes in the Processes for Current Source window. You can choose to have all processes expanded or collapsed.

#### Partner Tools and Web Browser

The display of the Partner Tools and Web Browser tab depends on whether you are running ISE on a personal computer or UNIX.

#### Partner Tools (Personal Computers Only)

The Partner Tools tab allows you to specify the location of third party executables.

#### Web Browser (UNIX Only)

The Web Browser tab allows you to specify the location of the browser used to view Web pages. By default, it is set to Netscape.

### **Displaying and Hiding Windows and Toolbars**

| Menu Item         | Function                                                                                                                     |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| Standard Toolbar  | Displays or hides the Standard toolbar.                                                                                      |

| Editor Toolbar    | Displays or hides the Editor toolbar.                                                                                        |

| Project Workspace | Displays or hides the Project<br>Workspace (the Sources in Project<br>window and the Processes for<br>Current Source window) |

| Sources           | Displays or hides the Sources in<br>Project window                                                                           |

| Processes         | Displays or hides the Processes<br>for Current Sources Window                                                                |

| Transcript        | Displays or hides the Transcript window                                                                                      |

| File Names        | Displays or hides the display of<br>file names in the Module View of<br>the Sources in Project window                        |

Click **View** to control the windows and toolbars you want to display:

| Menu Item            | Function                                                                       |  |  |

|----------------------|--------------------------------------------------------------------------------|--|--|

| Refresh F5           | Rebuilds the project hierarchy<br>and updates the Sources in<br>Project window |  |  |

| Minimize All Windows | Minimizes all ISE Windows                                                      |  |  |

To hide the window or toolbar, right-click to display the popupmenu, then click Hide (just below Allow Docking). To redisplay it, click that window or toolbar from the View menu. The Hide selection is on the source or process window context menu.

### **Docking and Undocking Windows and Toolbars**

Project Navigator allows you to dock and undock most windows and toolbars. You can remove windows and toolbars from the Project Manager interface and place and size them separately. See the Project Navigator online help for detailed information on docking and undocking windows and toolbars.

# **Snapshots and Archives**

To save a specific revision of your project, you can archive it or take a snapshot of it.

When you archive a project, you create a ZIP file for that version and place it in a specified directory. To archive a project, click  $Project \rightarrow Archive$  in Project Navigator. To open an archive or see the files in it, unzip it.

When you take a snapshot of a project, the snapshot becomes part of the project. It is accessible from the Snapshot View of the Sources in Project window. You can open it at any time to view its contents. If you replace the current project with a snapshot, you can make changes and reprocess the snapshot version of the project as desired. You can also replace the current version of a project with one captured previously as a snapshot.